Code: Alles auswählen

b a x b a y

0 0 0 0 1 0 1

1 0 0 1 1 1 0

2 0 1 0 1 0 0

3 0 1 1 1 1 1

4 1 0 0 0 1 1

5 1 0 1 1 1 0

6 1 1 0 1 0 0

7 1 1 1 1 0 0

b a x b

0 0 0 0 1

1 0 0 1 1

2 0 1 0 1

3 0 1 1 1

4 1 0 0 0

5 1 0 1 1

6 1 1 0 1

7 1 1 1 1

b a x a

0 0 0 0 0

1 0 0 1 1

2 0 1 0 0

3 0 1 1 1

4 1 0 0 1

5 1 0 1 1

6 1 1 0 0

7 1 1 1 0

b a x y

0 0 0 0 1

1 0 0 1 0

2 0 1 0 0

3 0 1 1 1

4 1 0 0 1

5 1 0 1 0

6 1 1 0 0

7 1 1 1 0

b a x b

0 0 0 0 1

1 0 0 1 1

2 0 1 0 1

3 0 1 1 1

5 1 0 1 1

6 1 1 0 1

7 1 1 1 1

b a x a

1 0 0 1 1

3 0 1 1 1

4 1 0 0 1

5 1 0 1 1

b a x y

0 0 0 0 1

3 0 1 1 1

4 1 0 0 1

b a x b

Gruppe 0:

0 0 0 0 1

Gruppe 1:

1 0 0 1 1

2 0 1 0 1

Gruppe 2:

3 0 1 1 1

5 1 0 1 1

6 1 1 0 1

Gruppe 3:

7 1 1 1 1

b a x a

Gruppe 1:

1 0 0 1 1

4 1 0 0 1

Gruppe 2:

3 0 1 1 1

5 1 0 1 1

b a x y

Gruppe 0:

0 0 0 0 1

Gruppe 1:

4 1 0 0 1

Gruppe 2:

3 0 1 1 1

b a x b

Gruppe 0:

0 0 0 0 1

Gruppe 1:

1 0 0 1 1

2 0 1 0 1

Gruppe 2:

3 0 1 1 1

5 1 0 1 1

6 1 1 0 1

Gruppe 3:

7 1 1 1 1

0;1 0 0 -

0;2 0 - 0

1;3 0 - 1

1;5 - 0 1

2;3 0 1 -

2;6 - 1 0

3;7 - 1 1

5;7 1 - 1

6;7 1 1 -

1;5 - 0 1

2;6 - 1 0

3;7 - 1 1

0;2 0 - 0

1;3 0 - 1

5;7 1 - 1

2;3 0 1 -

6;7 1 1 -

0;1 0 0 -

Gruppe 1:

1;5 - 0 1

2;6 - 1 0

Gruppe 2:

3;7 - 1 1

1;5;3;7 - - 1

2;6;3;7 - 1 -

Gruppe 0:

0;2 0 - 0

Gruppe 1:

1;3 0 - 1

Gruppe 2:

5;7 1 - 1

0;2;1;3 0 - -

1;3;5;7 - - 1

Gruppe 0:

0;1 0 0 -

Gruppe 1:

2;3 0 1 -

Gruppe 2:

6;7 1 1 -

0;1;2;3 0 - -

2;3;6;7 - 1 -

1;5;3;7 - - 1

2;6;3;7 - 1 -

0;2;1;3 0 - -

1;3;5;7 - - 1

0;1;2;3 0 - -

2;3;6;7 - 1 -

1;5;3;7 - - 1

1;3;5;7 - - 1

2;3;6;7 - 1 -

2;6;3;7 - 1 -

0;2;1;3 0 - -

0;1;2;3 0 - -

1;5;3;7 - - 1

2;3;6;7 - 1 -

0;1;2;3 0 - -

0 1 2 3 5 6 7

1;5;3;7 * * * *

2;3;6;7 * * * *

0;1;2;3 * * * *

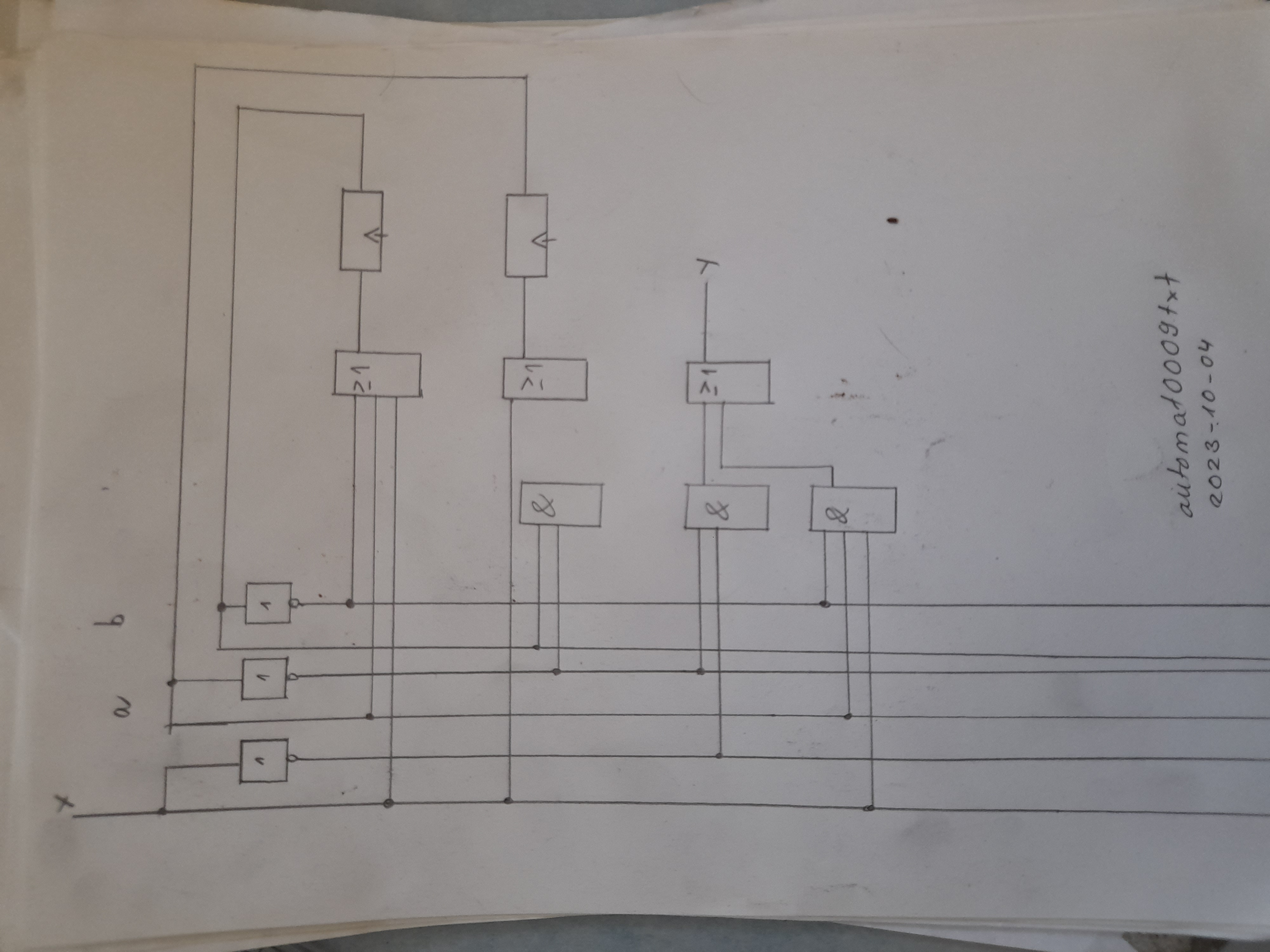

b <= (not b or a or x)

b a x a

Gruppe 1:

1 0 0 1 1

4 1 0 0 1

Gruppe 2:

3 0 1 1 1

5 1 0 1 1

1;3 - - 1

1;5 - 0 1

4;5 1 0 -

1 3 4 5

1;3 * *

1;5 * *

4;5 * *

1 3 4 5

1;3 * *

4;5 * *

a <= (x) or (b and not a)

b a x y

Gruppe 0:

0 0 0 0 1

Gruppe 1:

4 1 0 0 1

Gruppe 2:

3 0 1 1 1

0;4 - 0 0

3 0 1 1

y <= (not a and not x) or (not b and a and x)

b <= (not b or a or x)

a <= (x) or (b and not a)

y <= (not a and not x) or (not b and a and x)

Code: Alles auswählen

entity meinautomatenuebergangsnetz0001 is

port

(

bin, ain, x: in bit;

bout, aout: out bit

);

end;

entity meinautomatenausgangsschalnetz0001 is

port

(

bin, ain, x: in bit;

y: out bit

);

end;

entity rslatch0001 is

port

(

r, s: in bit;

q1, q2: inout bit

);

end;

architecture verhalten of meinautomatenuebergangsnetz0001 is

begin

bout <= (not bin or ain or x);

aout <= (x) or (bin and not ain);

end;

architecture verhalten of meinautomatenausgangsschalnetz0001 is

begin

y <= (not ain and not x) or (not bin and ain and x);

end;

architecture verhalten of rslatch0001 is

begin

q1 <= (r nor q2);

q2 <= (s nor q1);

end;